早年Intel(英特尔)发布Skylake架构时,官方就开始在高阶的HEDT平台开始调整原本的处理器快取记忆体结构,透过外媒《Wccftech》的发现,未来Intel的10nm Tiger Lake行动处理器可能也会具备如HEDT平台等级的快取记忆体。

这意味着,Intel 将正式将桌面、行动两种平台的快取内存条分开,过去行动版处理器仅只是桌面级降压的产品,快取记忆体包括L1、L2、L3 都与桌面级一样,这造成行动处理器普遍功耗表现不佳,而透过重新设计快取存储器的结构,未来Tiger Lake 行动处理器将有更好的处理效率。

据外媒分析,《Geekbench》跑分网站上所流出的Intel Tiger-YY 处理器,具备4 核8 线程,而每颗核心都具备1.25MB 超大的L2 快取,使L2 快取存储器的总数到达5MB 之多,L2 快取效率将大幅提升四倍,而L3 快取则是提升了50%,从原本的8MB 提高到12MB。

至于L1 快取,Intel 则是将L1 命令快取大小提高到48KB,L1 资料快取则是维持在32KB,经过快取记忆体的调整,新的Tiger Lake 行动处理器以增加L2 快取、不减少L3 快取的方式来提高整体性能,可以说在快取记忆体方面的架构整个翻新。

此外,新的Tiger Lake 也将步向AMD 处理器的后尘,加入PCIe 4.0 的支援,目前PCIe 4.0 仅有AMD X570 和TRX40 两个平台支援,加入PCIe 4.0 支援的Tiger Lake 将可更有效率的与高速记忆体相配合,《Wccftech》同时也指出Tiger Lake 可能会舍弃现有的UHD 核显,整合Intel 最新开发、多达96 计算单元的Intel Xe 核显芯片。

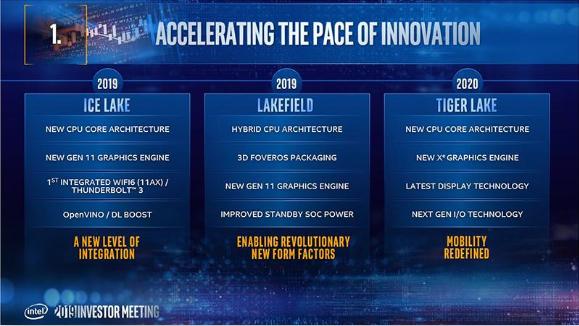

外媒估计Intel 第二款10nm 制程的Tiger Lake 处理器最快将于2020、2021 年投入消费市场,取代现有的Ice Lake 处理器,显然Intel 未来将更着重在行动平台而非桌面平台。

相关文章

- Intel推出Iris Xe MAX笔记本独立显卡,足以玩3A大作11-04

- Intel半导体制程还有重返荣耀的可能吗11-03

- 第11代Intel Core处理器正式登场,可以顺畅运行AAA游戏09-03

- Intel官方重新设计极简风格的logo有什么意义09-03

- Intel拿出数据证明自家处理器性能体验较佳08-19

- Intel第12 代Alder Lake情报走漏,18款产品大小核心自由配08-13

- Intel重申自家CPU拥有最佳游戏体验,热门作品FPS可超越对手10%以上08-08

- Intel将与更多游戏业者深度合作更提升处理器的游戏性能08-08

- Intel注册新商标,新品牌Evo同时曝光07-31

- Intel既有400系列主机板有条件使用第11代Core处理器,但只相容65W系列07-24

最新文章

热门文章

Intel双转轴、双屏幕概念机、与HP 如何解决超薄笔记本的USB Type-A 设计动眼看

Intel双转轴、双屏幕概念机、与HP 如何解决超薄笔记本的USB Type-A 设计动眼看 Intel发表NUC Element计画,借卡匣模组单板设计可相容从物联网到笔记型电脑等各类设计

Intel发表NUC Element计画,借卡匣模组单板设计可相容从物联网到笔记型电脑等各类设计 Intel:无内显主流处理器成固定品项,而且比较便宜

Intel:无内显主流处理器成固定品项,而且比较便宜- Intel与AMD合作的第8代Core i处理器G系列确定明年1月底停产

- Intel释出One API计画只要懂C++,就能简单打造跨硬体应用服务

- Intel研追踪运动员技术料2020东京奥运登场

- Dell发表XPS 13 2合1笔电搭载Intel第10代Core i系列处理器与翻转屏幕设计

- Intel宣布将在2020年推出全新独立显示卡「Xe」,至少有一组HDMI与三组DP输出

- Intel第9代Core i9-9900KS特别版桌机处理器,将以8组核心5.0 GHz涡轮加速频率运作

- 以数据说话Intel强调架构设计搭配制程技术,才能发挥处理器真正效能